Rio Yokota Weigang Wu (Eds.)

# **Supercomputing Frontiers**

4th Asian Conference, SCFA 2018 Singapore, March 26–29, 2018 Proceedings

# **Lecture Notes in Computer Science**

10776

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison

Lancaster University, Lancaster, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Zurich, Switzerland

John C. Mitchell

Stanford University, Stanford, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

C. Pandu Rangan

Indian Institute of Technology Madras, Chennai, India

Bernhard Steffen

TU Dortmund University, Dortmund, Germany

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Gerhard Weikum

Max Planck Institute for Informatics, Saarbrücken, Germany

More information about this series at http://www.springer.com/series/7407

Rio Yokota · Weigang Wu (Eds.)

# Supercomputing Frontiers

4th Asian Conference, SCFA 2018 Singapore, March 26–29, 2018 Proceedings

Editors

Rio Yokota

Tokyo Institute of Technology

Tokyo

Japan

Weigang Wu

Sun Yat-sen University

Guangzhou

China

ISSN 0302-9743 ISSN 1611-3349 (electronic) Lecture Notes in Computer Science ISBN 978-3-319-69952-3 ISBN 978-3-319-69953-0 (eBook) https://doi.org/10.1007/978-3-319-69953-0

Library of Congress Control Number: 2018937379

LNCS Sublibrary: SL1 - Theoretical Computer Science and General Issues

© The Editor(s) (if applicable) and The Author(s) 2018, corrected publication 2018. This book is an open access publication.

**Open Access** This book is licensed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license and indicate if changes were made.

The images or other third party material in this book are included in the book's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the book's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by the registered company Springer International Publishing AG part of Springer Nature

The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

#### **Preface**

As the share of supercomputers in Asia continues to increase, the relevance of supercomputing in Asia has achieved a critical mass to merit the inauguration of a supercomputing conference for Asia. Supercomputing Asia (SCA) 2018 encompassed an umbrella of notable supercomputing events with the key objective of promoting a vibrant and relevant HPC ecosystem in Asian countries, and was held during March 26–29, 2018, at Resorts World Convention Centre, Singapore.

The technical program of SCA18 had its roots in Supercomputing Frontiers (SCF), which is Singapore's annual international HPC conference that provides a platform for leaders from both academia and industry to interact and discuss visionary ideas, important global trends, and substantial innovations in supercomputing. The conference was inaugurated in 2015 and helmed by A\*STAR Computational Resource Centre (A\*CRC). In March 2017, the National Supercomputing Centre (NSCC) Singapore took over hosting of Supercomputing Frontiers 2017 (SCF17). NSCC was established in 2015 and manages Singapore's first national petascale facility with available HPC resources to support science and engineering computing needs for academic, research, and industry communities. SCF17 was attended by over 450 delegates from over 12 different countries.

Riding on the success from the previous year, the SCA18 program highlights will included:

- HPC technology updates and case studies

- Scientific paper presentations

- Academic activities and workshop for students

The co-located HPC events include:

- Asia-Pacific Advanced Network Meeting (APAN45)

- Towards an Asia Research Platform (ARP)

- Conference on Next-Generation Arithmetic (CoNGA)

- Singapore-Japan Joint Sessions

- Supercomputing Frontiers Asia (SCFA)

SCFA represented the technical program for SCA18, consisting of four tracks:

- Application, Algorithms, and Libraries

- Programming and System Software

- Data, Storage, and Visualization

- Architecture, Network/Communications, and Management

#### VI Preface

We would like to express our gratitude to all our colleagues for submitting papers to the SCA18 scientific sessions, as well as to the members of the Program Committee for organizing this year's attractive program.

March 2018 Rio Yokota Weigang Wu

## **Organization**

#### **Technical Program Committee**

#### **Technical Papers Co-chairs**

Rio Yokota Tokyo Institute of Technology, Japan Weigang Wu Sun Yat-sen University, China

#### Application, Algorithms, and Libraries

Inria, France Emmanuel Agullo

Ariful Azad Lawrence Berkeley National Laboratory, USA

Costas Bekas IBM, Switzerland

Aparna Chandramowlishwaran University of California Irvine, USA

NVIDIA, USA Kate Clark

Hal Finkel Argonne National Laboratory, USA Michael Heroux Sandia National Laboratories, USA

Simula, Norway Johannes Langguth

Piotr R. Luszczek University of Tennessee at Knoxville, USA Maciej Malawski AGH University of Science and Technology,

Poland

John Owens UC Davis, USA

University of the Pacific, USA Vivek Pallipuram

Antonio Pena Barcelona Supercomputing Center, Spain Argonne National Laboratory, USA Min Si

Hari Sundar University of Utah, USA

Nathan Tallent Pacific Northwest National Laboratory, USA

#### **Programming and System Software**

Olivier Aumage Inria, France

Sunita Chandrasekaran University of Delaware, USA Florina M. Ciorba University of Basel, Switzerland King Abdullah University of Science Bilel Hadri

and Technology, Saudi Arabia

Zbigniew Kalbarczyk University of Illinois, USA

Hatem Ltaief King Abdullah University of Science

and Technology, Saudi Arabia

Oak Ridge National Laboratory, USA Arthur Maccabe

Naoya Maruyama Lawrence Livermore National Laboratory, USA

Ronald Minnich Google Inc., USA

University of Bordeaux, France Raymond Namyst

C. J. Newburn NVIDIA, USA Christian Perez Inria, France

#### VIII Organization

Miquel Pericas Chalmers University of Technology, Sweden Mohamed Wahib National Institute of Advanced Industrial Science

and Technology, Japan

#### Data, Storage, and Visualization

Janine Bennett Sandia National Laboratories, USA Mahdi Bohlouli University of Koblenz, Germany Steffen Frey University of Stuttgart, Germany

Shadi Ibrahim Inria, France

Hai Jin Huazhong University of Science and Technology,

China

Hideyuki Kawashima University of Tsukuba, Japan

Quincey Koziol Lawrence Berkeley National Laboratory, USA

Suzanne McIntosh New York University, USA Bogdan Nicolae Huawei Technologies, China

David Pugmire Oak Ridge National Laboratory, USA

Shinji Sumimoto Fujitsu, Japan

Bronis R. de Supinski Lawrence Livermore National Laboratory, USA

Daniela Ushizima Lawrence Berkeley National Laboratory, USA

Jon Woodring Los Alamos National Laboratory, USA

Amelie Chi Zhou Inria, France

#### Architecture, Network/Communications, and Management

David Abramson The University of Queensland, Australia

Eishi Arima The University of Tokyo, Japan

Ali R. Butt Virginia Tech, USA

Nikhil Jain University of Illinois, USA

John Kim Korea Advanced Institute of Science

and Technology, Korea

John Shalf Lawrence Berkeley National Laboratory, USA

Ryota Shioya Nagoya University, Japan

Jeremiah J. Wilke Sandia National Laboratories, USA Weikuan Yu Florida State University, USA

# **Contents**

| Big | Data |

|-----|------|

|     |      |

| HHVSF: A Framework to Accelerate Drug-Based High-Throughput Virtual Screening on High-Performance Computers  Pin Chen, Xin Yan, Jiahui Li, Yunfei Du, and Jun Xu | 3   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| HBasechainDB – A Scalable Blockchain Framework on Hadoop Ecosystem                                                                                               | 18  |

| DETOUR: A Large-Scale Non-blocking Optical Data Center Fabric                                                                                                    | 30  |

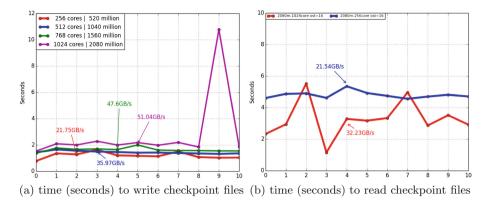

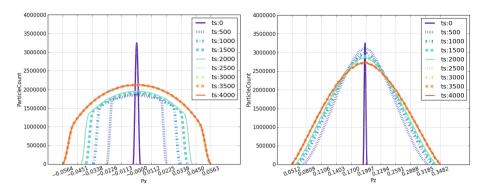

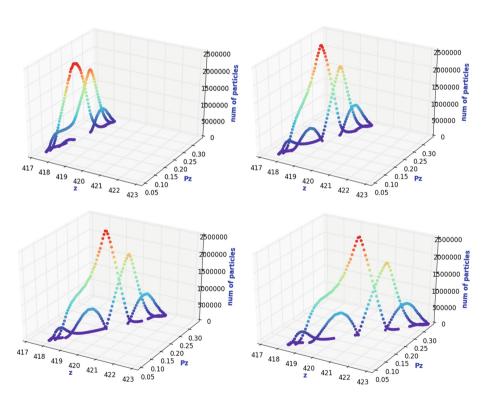

| Querying Large Scientific Data Sets with Adaptable IO System ADIOS<br>Junmin Gu, Scott Klasky, Norbert Podhorszki, Ji Qiang,<br>and Kesheng Wu                   | 51  |

| On the Performance of Spark on HPC Systems: Towards a Complete Picture                                                                                           | 70  |

| Experiences of Converging Big Data Analytics Frameworks with High Performance Computing Systems                                                                  | 90  |

| GPU/FPGA                                                                                                                                                         |     |

| MACC: An OpenACC Transpiler for Automatic Multi-GPU Use                                                                                                          | 109 |

| Acceleration of Wind Simulation Using Locally Mesh-Refined Lattice Boltzmann Method on GPU-Rich Supercomputers                                                   | 128 |

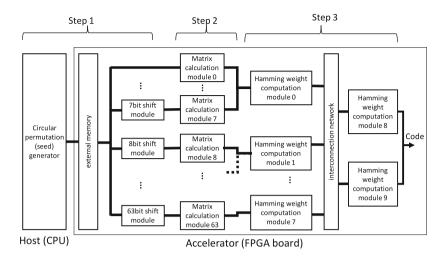

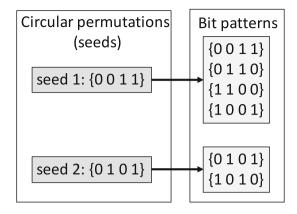

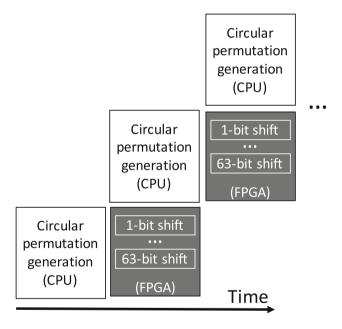

| Architecture of an FPGA-Based Heterogeneous System for Code-Search Problems                                                                                      | 146 |

### **Performance Tools**

| TINS: A Task-Based Dynamic Helper Core Strategy for In Situ Analytics                                                                                                                                                                                                                                      | 159 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Machine Learning Predictions for Underestimation of Job Runtime on HPC System                                                                                                                                                                                                                              | 179 |

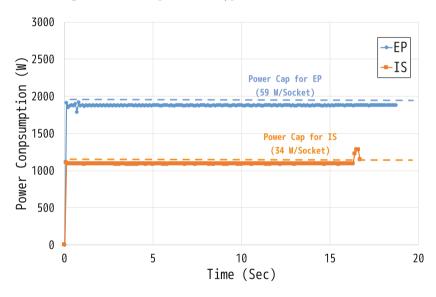

| A Power Management Framework with Simple DSL for Automatic Power-Performance Optimization on Power-Constrained HPC Systems Yasutaka Wada, Yuan He, Thang Cao, and Masaaki Kondo                                                                                                                            | 199 |

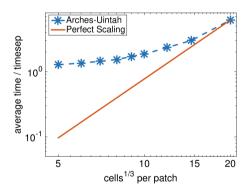

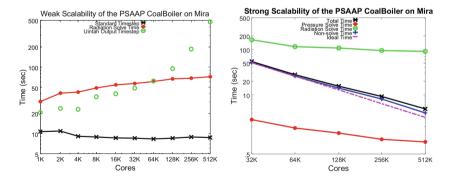

| Scalable Data Management of the Uintah Simulation Framework for Next-Generation Engineering Problems with Radiation Sidharth Kumar, Alan Humphrey, Will Usher, Steve Petruzza, Brad Peterson, John A. Schmidt, Derek Harris, Ben Isaac, Jeremy Thornock, Todd Harman, Valerio Pascucci, and Martin Berzins | 219 |

| Linear Algebra                                                                                                                                                                                                                                                                                             |     |

| High Performance LOBPCG Method for Solving Multiple Eigenvalues of Hubbard Model: Efficiency of Communication Avoiding Neumann Expansion Preconditioner                                                                                                                                                    | 243 |

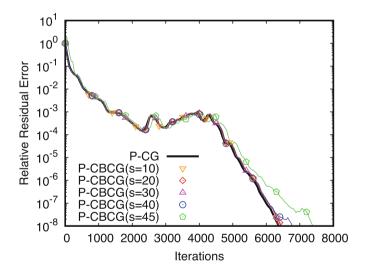

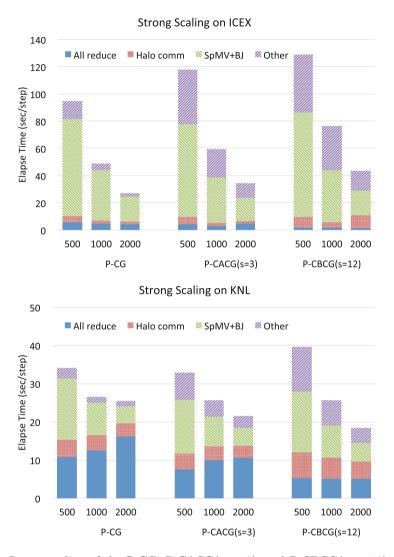

| Application of a Preconditioned Chebyshev Basis Communication-Avoiding Conjugate Gradient Method to a Multiphase Thermal-Hydraulic CFD Code                                                                                                                                                                | 257 |

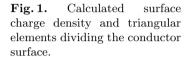

| Optimization of Hierarchical Matrix Computation on GPU                                                                                                                                                                                                                                                     | 274 |

| Erratum to: Machine Learning Predictions for Underestimation of Job Runtime on HPC System                                                                                                                                                                                                                  | E1  |

| Author Index                                                                                                                                                                                                                                                                                               | 293 |

# HHVSF: A Framework to Accelerate Drug-Based High-Throughput Virtual Screening on High-Performance Computers

Pin Chen<sup>1</sup>, Xin Yan<sup>1</sup>, Jiahui Li<sup>1</sup>, Yunfei Du<sup>1,2(⋈)</sup>, and Jun Xu<sup>1(⋈)</sup>

National Supercomputer Center in Guangzhou and Research Center for Drug Discovery, School of Data and Computer Science and School of Pharmaceutical Sciences, Sun Yat-Sen University, 132 East Circle at University City, Guangzhou 510006, China yunfei.du@nscc-gz.cn, junxu@biochemomes.com

School of Computer Science, National University of Defense Technology, Changsha 410073, China

Abstract. The High-performance High-throuhput Virtual Screening Framework (HHVSF) has been developed to accelerate High-Throughput Virtual Screening (HTVS) on high-performance computers. Task management and data management are two core components in HHVSF. Fine-grained computing resources are configured to support serial or threaded applications. Each task gets the input file from database through a preemptive algorithm and the failed tasks can be found and corrected. NoSQL database MongoDB is used as the data repository engine. Data is mobilized between the RAMDISK in computing node and the database. Data analysis is carried out after the computing process, and the results are stored in the database. Among the most popular molecular docking and molecular structure similarity packages, Autodock vina (ADV) and WEGA were chosen to carry out experiments. Results show that when ADV was used for molecular docking, 10 million molecules were screened and analyzed in 22.31 h with 16000 cores, and the throughput reached up to 1324 molecules per second, averaging 145 molecules per second during the steady-running process. For WEGA, 958 million conformations were screened and analyzed in 34.12 min with 4000 cores, of which throughput reached up to 9448 molecules per second, 6430 molecules per second on average.

**Keywords:** High-Throughput Virtual Screening · Drug discovery High-Performance Computing · Molecular docking Molecular structure similarity

#### 1 Introduction

Computational methodology has become a significant component in pharmaceutical industry for drug design and discovery [1–4]. Typically, molecular docking and molecular structure similarity are two frequently used computational approaches. High-Throughput Virtual Screening (HTVS) is known to computationally screen large compound libraries. These libraries contain a huge number of small-molecules varying

from tens of thousands to millions, require a high volume of lots-of-small files scenario for a virtual screening campaign. With the development of high-performance computers, the virtual drug screening is accelerating. However, HTVS still faces challenges while a large scale virtual screening application is executed on High-Performance Computing (HPC) resources, such as distributing massive tasks, analyzing lots-of-small molecular structure files, and implementing fault tolerance.

Tools have been developed to accelerate the process of HTVS on HPC resources. Falkon [5] is a lightweight execution framework to enable loosely coupled program to run on peta-scale systems. The benchmark [6] shows that DOCK5 can scale up to 116,000 cores with high efficiency by Falkon. VinaMPI is a MPI version program based on ADV package, which uses a large number of cores to speed-up individual docking tasks. VinaMPI successfully ran on 84,672 cores on Kraken supercomputer and efficiently reduce the total time-to-completion. While all the above works focus on performance and efficiency of distributing tasks, ignoring the whole HTVS process, for instance, robustness, recoverability and result analysis. FireWorks (FWS) [7] is a workflow software for high-throughput calculation running on supercomputer, effectively solve the problem of concurrent task distribution and fault tolerance management, and provide an intuitive graphical interface. However, FWS pays more attention on versatility and usability. DVSDMS [8] is a distributed virtual screening data management system, only focusing on high-throughput docking process in the data management issues. Therefore, the architecture of high-performance computers, as well as the computational characteristics of the application, needs to be considered to design the framework for HTVS on high-performance computers.

In this work, we report a general framework - High-performance High-throughput Virtual Screening Framework (HHVSF) - to enable large-scale, multitasking and small-size input and output (IO) applications to efficiently execute on HPC resources. This framework contains task management and data management systems, which can handle thousands of tasks, manage a large volume of lots-of-small files, and reduce the long processing time for analyzing. The purpose of HHVSF is to provide high computational performance based on portability, availability, serviceability and stability (PASS).

## 2 Experimental and Computational Details

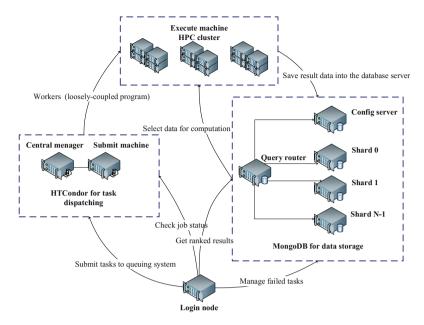

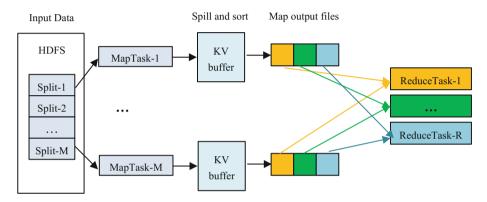

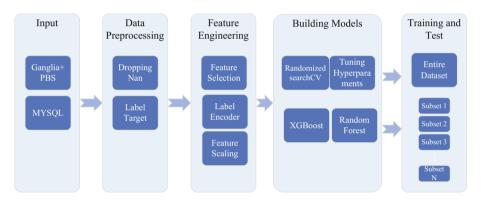

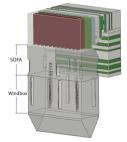

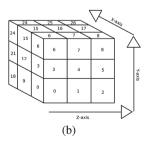

The framework of HHVSF is comprised of two parts: task management and distributed data management (see Fig. 1). In order to access and store data efficiently and flexibly, the executions of a program are coupled loosely by MongoDB C driver, while the application codes do not need to be modified. The following three subsections document the overall framework of HHVSF, the simulation parameters and the data sets of the experiments are introduced at the end of this section. ADV [9] and WEGA [10] are chosen as typical applications to carry out the experiments, and others can be integrated into the HHVSF in similar way.

Fig. 1. The hardware and relevant operations in HHVSF.

#### 2.1 Task Management

The followings are mainly considered in the task management system: two-level task scheduling, preemptive scheduling algorithm for worker and failed tasks recovery.

#### 2.1.1 Task Scheduling

HTVS employs massive computing resources to support a large number of independent computing tasks. Because most molecular docking and molecular structure similarity tools, for instance, ADV, Gold [11], Glide [12], FlexX [13] and WEGA, are serial or threaded codes, these computing tasks are typical fine-grained Many-Task Computing (MTC) [6]. Such MTC tasks cannot take full advantage of the static scheduling solution with coarse scheduling granularity, while most traditional large-scale HPC resources are configured with coarse scheduling granularity under a control of batch queuing system such as Simple Linux Utility for Resource Management (SLURM) [14], Portable Batch System (PBS)/Torque [15], and Sun Grid Engine (SGE) [16].

Multi-level scheduling method can effectively solve the different application requirements for scheduling granularity, while maintaining the unified management of computing resources. The first level scheduler applies for a number of resources to the second level for task distribution. The second level scheduler can refine the computing resources and then distributes the tasks. HTCondor [17] is chosen to be the second level scheduler to dispatch tasks. HTCondor is full-featured batch workload management system for coordinating a large number of independent serial or parallel jobs in High-Throughput Computing (HTC) environment. We configure the HTCondor with one core per slot to provide more flexible task scheduling.

#### 2.1.2 Preemptive Scheduling Algorithm

Algorithm for vina wrapper

Molecular docking and molecular structure similarity are typical MTC applications, while maintaining millions of tasks by HTCondor to screen a large database with millions of ligands or conformers is still a touch work. Thus, we transform MTC into HTC by wrapping ADV or WEGA program with MongoDB C driver (version 1.4.2) as a worker. Each worker accesses database preemptively to get input files until all data is traversed. MongoDB provides atomic operation with "inc" to ensure data security when multitudinous workers start concurrently, so that each worker can get unique job. After the worker obtains data from the database, the data is written to a file and stored on the local file system implemented in RAMDISK. The kernel function's computational procedure is shown in the Fig. 2.

```

1:index id \leftarrow 1

2:while index id ≤ ligand count

3: //atomic increment operation

do index id \leftarrow index id + 1

5:

get pdbqt file from database (index id)

6:

execute (vina.exe)

7:

analyze (output)

8:

insert database (score,conformation,status tag)

9:

remove(temporary files)

10:end

Algorithm for wega wrapper

1: index id \leftarrow1

2:while index id \leq sd file count

3: //atomic increment operation

4:

do index id \leftarrow index id + 1

5:

get sd file from database (index id)

6:

execute (wega.exe)

7:

analyze (output)

8:

insert database (score,conformation,status tag)

9:

remove (temporary files)

10:end

```

Fig. 2. The pseudo code of vina\_wrapper and wega\_wrapper.

#### 2.1.3 Fault Tolerance

Fault tolerance in this context can be simplified as the ability to automatically restart a task when the original run fails. When the HTVS scales to millions of tasks or run a long-time task, it is easy to get failures for bad input parameters, such as computing node fault, IO blocking, and network latency. There are two ways to consider fault

tolerance in this case, one is monitoring the job status during the running by job management system, another is making a successful or failed tag on each task after the task is finished. HTCondor provides checkpoint mechanism in the standard universe by using condor\_compile to relink the execution with the HTCondor libraries, while those coupled program vina\_wrapper and wega\_wrapper, containing system calls like system (), cannot provide check pointing services with HTCondor. As a result, we choose the second method. When a worker calls the execution of ADV or WEGA successfully, a tag that represents the task status will insert into the corresponding document in MongoDB database. After the job is finished, it needs to check the document's failed tag and then restart the failed jobs.

#### 2.2 Data Management

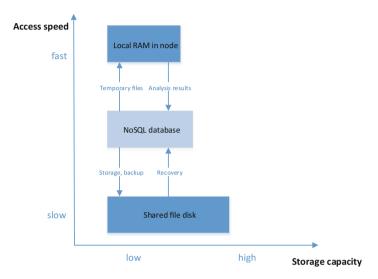

Data storage, data relocation and data analysis are the bottlenecks when a virtual screening is scaled up to handle millions of tasks on thousands of cores. Such scattered lots-of-small files can overburden the shared file system with abundant IO operations if the plain files are accessed and stored directly. Database offers an attractive solution to both the storage and the data querying. In our framework, we avoid using shared file system by replacing it with the combination of MongoDB and local RAMDISK. The IO files are stored in MongoDB, while they are cached in the local RAMDISK during computation. The following three subsections describe the details on the data storage, data relocation and data analysis in HHVSF.

#### 2.2.1 NoSQL Database for Storage

Chemical databases are the critical components of HTVS, which provide the basic information to build knowledge-based models for discovering and designing drug. Such as, PubChem [18], ZINC [19], ChEMBL [20], ChemDB [21], contain millions of compounds, provide shape data, physical properties, biological activities, and other information for pharmaceutical evaluations. Currently, many molecular docking programs and molecular structure similarity algorithms read the input and store the output in plain text files, which is not suitable for management when data grow up rapidly. Maintaining and analyzing such data are difficult.

MongoDB [22] is used as the data repository engine, which is a high performance, high availability, automatic scaling, open source NoSQL (Not Only SQL) database. This architecture is suitable for sparse and document-like data storage. By using MongoDB "index", molecules can be queried and ranked easily. In addition, MongoDB uses "sharding" (a method for distributing data across multiple machines) to support deployments with large data sets in high throughput manner, enhancing the computational performance by balancing query loading as the database growing. Finally, MongDB accepts big data up to 16 MB. MongDB is employed for WEGA to access the big conformation SDF input file.

#### 2.2.2 Data Relocation

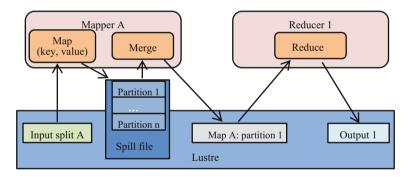

ADV and WEGA involve in processing large sized plain text files. Without modifying their source codes, the programs have to process huge number of small molecular structure files by moving on the shared file disks when screening a large-scale

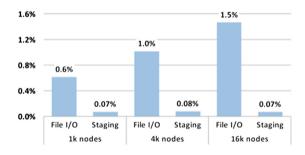

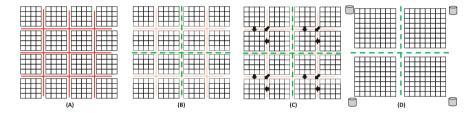

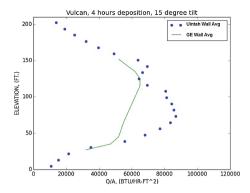

compound library. Hence, the RAMDISK in computing nodes are used to temporarily store the IO files needed by the applications (see Fig. 3). The RAMDISK provides high-speed, low-latency IO operations for handling lots-of-small files, while the high storage capacity of shared file disk is still fully occupied to store the resulting data. By relocating data between MongDB and RAMDISK, the IO pressure for shared file storage is effectively mitigated.

Fig. 3. The flowchart of the data relocation.

#### 2.2.3 Data Analysis

For virtual screening using molecular docking and molecular structure similarity approaches, scores and molecular similarities have to be calculated before ranking the molecules in a large sized compound library. In consideration of high-performance computing systems with shared file storage, it is necessary to avoid IO overloading problems which are caused by a great number of small files. Thus, it is not wise to analyze the output files on the shared storage disk. When the computations are accomplished in the RAMDISK, the output files are analyzed and the compounds in the library are ranked based upon scores or similarities. This protocol minimizes the IO stress when the number of small files increases dramatically.

#### 2.3 Simulation Parameters and Data Sets

#### 2.3.1 ADV

About twenty million ligands with mol2 format file were obtained from ZINC database FTP server (http://zinc.docking.org/db/bysubset/6/). The pymongo (version 3.2.1) Python library was used for database operations. A python script was developed to

insert mol2 files into MongoDB. MGLTools (version 1.5.6) was used to convert mol2 files into pdbqt file for docking. We prepared five different sized data sets (from zinc\_ligand\_ $1 \sim 5$ ), as shown in Table 2. All data sets are sorted by heavy atom number arranged in ascending order. After finishing molecular docking, the result pdbqt file format was converted to mol file format by Open Babel package [23] (version 2.4.0).

The protein target is a crystal structure of the alpha subunit of glycyl tRNA synthetase (PDB codes: 5F5 W). The (x, y, z) coordinates (in Å) for the center of the docking site is (-94.666, 51.401, 8.991), and the side of the cubic box is (14, 18, 12). The argument of num\_modes is set to 1.

#### 2.3.2 WEGA

A SDF file containing about twenty million molecules was obtained from ZINC database FTP server. Approximately 958 million conformers were generated from the SDF file using the CAESAR algorithm [24] in discovery studio (version 3.5) [25] for shape-feature similarity calculation. In order to take advantage of the 16 MB storage space in MongoDB, the conformer files were split into smaller files which occupied 15 MB for each file, and then inserted into the database. Table 2 gives two data sets for WEGA (zinc\_conformer\_1 and zinc\_conformer\_2).

The query molecule is 4-amino-1-[4,5-dihydroxy-3-(2-hydroxyethyl)-1-cyclopent-2-enyl]-pyrimidin-2-one (ZINC ID: ZINC03834084). The method for molecular overlay is set to 2 (combing the shape similarity and pharmacophore similarity). Each SDF file corresponds up to 100 similar molecules. The Table 1 shows the detailed information of the data sets which are used throughout the article.

**Table 1.** Data sets for testing. The zinc\_ligand\_ $1 \sim 5$  databases are prepared for Audock\_vina, the zinc\_ligand\_ $2 \sim 5$  databases were extracted from zinc\_ligand\_1 in accordance with a certain proportion. The zinc\_conformer\_ $1 \sim 2$  databases are prepared for WEGA, and the zinc\_conformer\_2 are extracted from zinc\_conformer\_1 randomly.

| Database name    | Number             | Description                                                        |

|------------------|--------------------|--------------------------------------------------------------------|

| zinc_ligand_1    | 20430347           | ZINC purchasable subset                                            |

| zinc_ligand_2    | 107                | Enumerate one from every 2 molecules of ZINC purchasable subset    |

| zinc_ligand_3    | 10 <sup>6</sup>    | Enumerate one from every 20 molecules of ZINC purchasable subset   |

| zinc_ligand_4    | 10 <sup>5</sup>    | Enumerate one from every 200 molecules of ZINC purchasable subset  |

| zinc_ligand_5    | 104                | Enumerate one from every 2000 molecules of ZINC purchasable subset |

| zinc_conformer_1 | $\sim 9.58 * 10^8$ | Up to 50 conformers per molecule of ZINC purchasable subset        |

| zinc_conformer_2 | $\sim 10^6$        | Up to 50 conformers per molecule of ZINC purchasable subset        |

All tests run on Tianhe-2 (MilkyWay-2) supercomputer, which consists of 16,000 computing nodes connected via the TH Express-2 interconnect. Each computing node is equipped with two Intel Xeon E5-2692 CPUs (12-core, 2.2 GHz), and configured with 64 GB memory. The storage subsystem contains 64 storage servers with a total capacity of 12.4 PB. The LUSTRE storage architecture is used as a site-wide global file system.

#### 3 Results and Discussion

#### 3.1 Load Balance

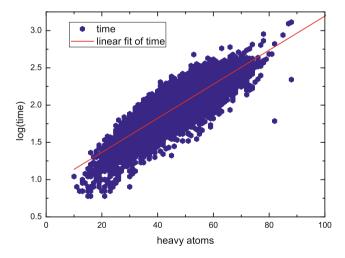

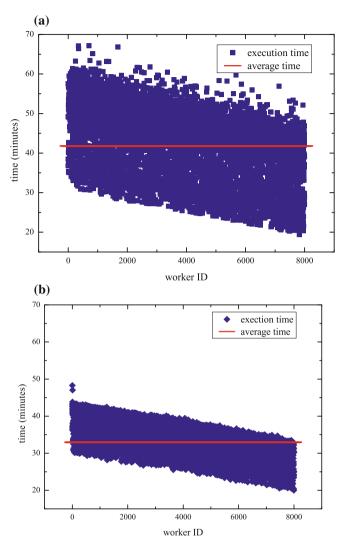

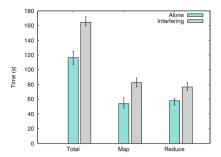

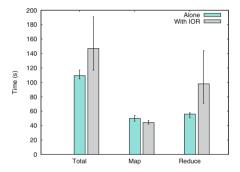

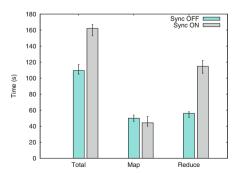

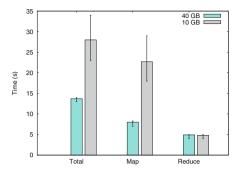

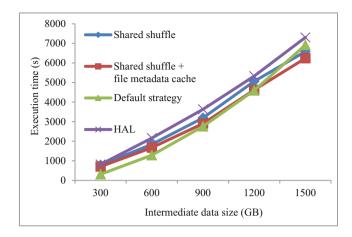

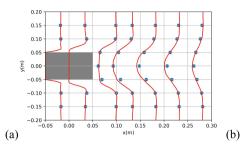

Time for screening a compound ranges from minutes to hours depending on the complexity of the molecular structure. Reports [9, 26] indicate that the compound complexity, for instance, number of active torsions or number of heavy atoms, dominates the computing time of molecular docking. In order to determine the relation between the number of heavy atoms computing time and the computing complexity, the zinc\_lignad\_5 data set was chosen to record the number of heavy atom in a ligand and computing time, as depicted in Fig. 4. The number of heavy atoms presents a linear relationship with time (logarithmic form), which indicates more heavy atoms in a small molecule requires longer computing time. For zinc\_ligand\_2~5 data sets are scaled down from zinc\_ligand\_1 by a certain percentage, the other data sets will also benefit from this approach. Based on this information, the zinc\_ligand\_4 data set was tested on 8,000 cores. Figure 5a and b demonstrate that the average computing time per worker is reduced by 8.83 s when load balancing protocol was used.

**Fig. 4.** The number of heavy atoms in a compound (x-axis), the computing time (logarithmic form) of a molecular docking (y-axis). The results are based upon zinc\_ligand\_5 data set.

**Fig. 5.** (a) The computing time of each worker without load balancing. The red line is the average computing time per task. (b) The computing time per worker with load balance. The red line is the average computing time per task. (Color figure online)

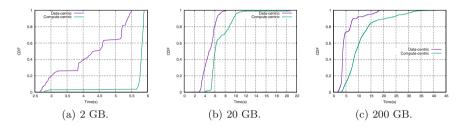

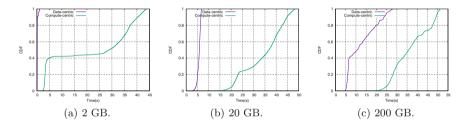

#### 3.2 Throughput with Data

The MongoDB monitors the status of a running instance. When a worker starts, a "connection" operation is activated by MongoDB's server. After the computing task is

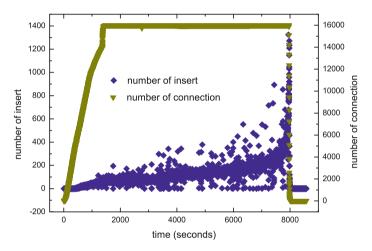

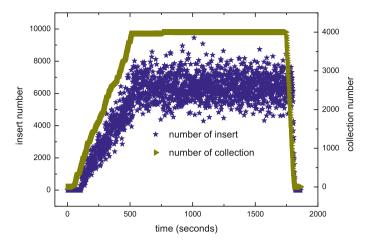

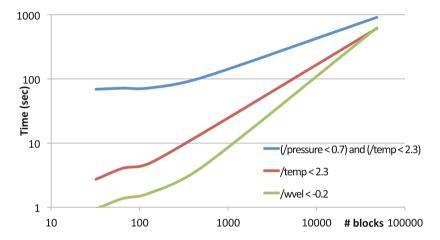

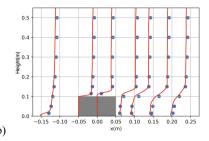

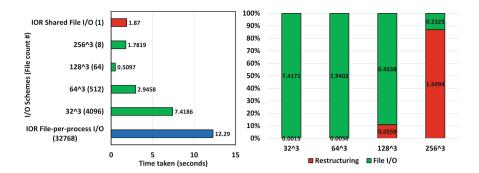

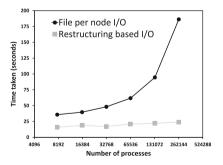

accomplished, the resulting data (score, structural conformation, and running status) will be inserted into MongoDB's collection. Figure 6 shows the "connection" and "insert" operations of MongoDB's server every second with vina\_wrapper during the whole computing period, the points of inverted triangle clearly reveal the three stages of running tasks: startup, steady-running and finish. The total time during the startup was 1,396 s to start 16,000 workers, averaging 11 tasks per second. The points of rhombus become higher gradually as time progresses, reaching up to 1,324 molecules per second and averaging 145 molecules per second. Table 2 gives the results for other data sets. As for WEGA, Fig. 7 shows that the data throughput can reach up to 9,448 molecules per second, averaging 6,430 molecules per second, indicating a high performance and a high data throughput.

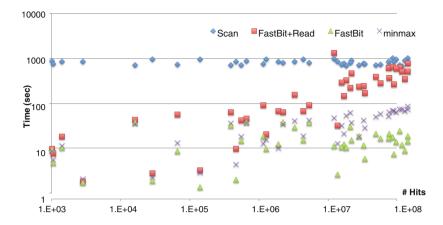

**Fig. 6.** The number of "insert" operation and "connection" operation in MongoDB's server when running ADV application. The zinc\_ligand\_3 data set was used to run on 16,000 cores.

| Program | Program Test Cores |       | Startup         | Maximum data       | Average data       |

|---------|--------------------|-------|-----------------|--------------------|--------------------|

|         | number             |       | time throughput |                    | throughput         |

|         |                    |       | (second)        | (molecules/second) | (molecules/second) |

| ADV     | 107                | 16000 | 1222            | 1957               | 130                |

| ADV     | 10 <sup>6</sup>    | 16000 | 1396            | 1324               | 145                |

| ADV     | 10 <sup>5</sup>    | 8000  | 564             | 473                | 76                 |

| WEGA    | 95712              | 4000  | 313             | 9448               | 6430               |

Table 2. Data throughput for ADV and WEGA on different data sets.

**Fig. 7.** The number of "insert" operation and "connection" operation in MongoDB's server when running WEGA application. The zinc\_conformer\_1 data set was used to run on 4,000 cores.

#### 3.3 Scalability

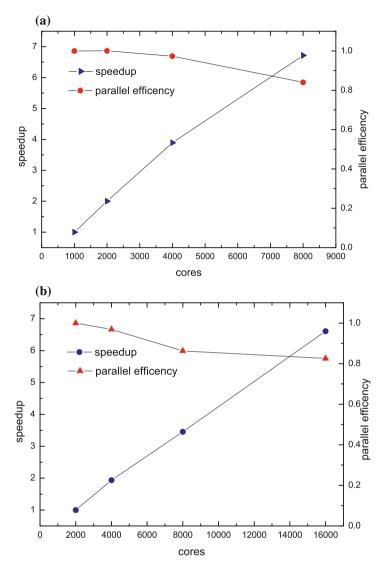

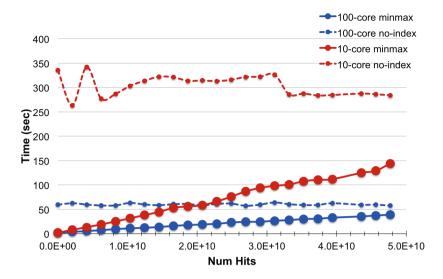

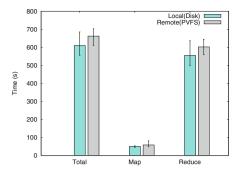

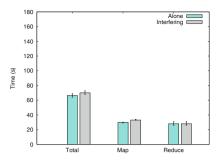

To test scalability, we perform the experiments of speedup and parallel efficiency with zinc\_ligand\_4 data set and zinc\_ligand\_3 data set. Figure 8a shows zinc\_ligand\_4 data set can be scaled to 8,000 cores with parallel efficiency of 0.84, and the zinc\_ligand\_4 data set can be scaled to 16,000 cores with parallel efficiency of 0.83 (see Fig. 8b). It is shown that the parallel efficiency decreases sharply when computing resource is scaled up to more than 8,000 cores. This is because more cores represent more workers, and thus, more time will be cost by HTCondor to start those workers.

#### 3.4 Fault Tolerance

Fault tolerance management can avoid task failures due to external environments, for instances, compute node fault, network blocking, IO latency, etc. Table 3 gives the information of failed tasks on different data sets. The zinc\_ligand\_2 data set has a high failure rate than others due to ten million ligands containing more ligands with high molecular weight which are not suitable for docking space of the protein (PDB code: 5W5F). In addition, longer calculations can lead to higher failures. The zinc\_conformer\_1 data set has fewer files (95712 SDF files in total) and less computing time, as a result, produces a low failure rate.

**Fig. 8.** (a) Speedup (right triangle) and parallel efficiency (read dot) of molecular docking experiment on zinc\_ligand\_4 data set. (b) Speedup (block dot) and parallel efficiency (upper triangle) of molecular docking experiment on zinc\_ligand\_3 data set.

Table 3. The failure rate and computing time for ADV and WEGA on different data sets.

| Program | Data set         | Cores | Failure rate | Last task time | Average time |

|---------|------------------|-------|--------------|----------------|--------------|

| ADV     | zinc_ligand_2    | 16000 | 0.01171      | 22.31 h        | 20.14 h      |

| ADV     | zinc_ligand_3    | 16000 | 0.00390      | 3.34 h         | 2.43 h       |

| ADV     | zinc_ligand_4    | 8000  | 0.00001      | 48.10 min      | 31.31 min    |

| WEGA    | zinc_conformer_1 | 4000  | 0.00002      | 34.12 min      | 28.20 min    |

#### 4 Conclusions

HHVSF includes task management and relocating data management, and supports the high-throughput applications of large-scale, multitasking and small sized IO files running on HPC resources. There are two types of virtual drug screening applications: computation-intensive applications (such as molecular docking). (2) data-intensive applications (such as molecular structure similarity based virtual screening campaigns). With HHVSF, two types of applications can run on Tianhe-2 supercomputer with high performance. Testing results show that when use ADV for molecular docking, the protein target (PDB code: 5W5F) was used to screen nearly half of compounds from the ZINC database within one day on 16,000 cores. For WEGA, 958 million conformations were screened by using about a half hour on 4,000 cores. The ranked ligands or conformers can be accessed in milliseconds by specifying the "sort" method from the database. Meanwhile, the IO pressure of shared file storage affected by lots-of-small files in HPC resources can be mitigated. Thus, HHVSF can significantly accelerate HTVS campaigns on HPC resources.

**Acknowledgments.** We would like to thank Prof. Xin Yan for permission to use WEGA program to test. Helpful discussions with Guixin Guo, Lin Li, Wen Wan and technical assistance by HTCondor Team (University of Wisconsin-Madison) are gratefully acknowledged. This work was performed by the auspices of the NSFC (U1611261), GD Frontier & Key Techn, Innovation Program (2015B010109004).

#### References

- Manglik, A., Lin, H., Aryal, D.K., Mccorvy, J.D., Dengler, D., Corder, G., Levit, A., Kling, R.C., Bernat, V., Hübner, H.: Structure-based discovery of opioid analgesics with reduced side effects. Nature 537(7619), 1 (2016)

- 2. Rodrigues, T., Reker, D., Schneider, P., Schneider, G.: Counting on natural products for drug design. Nat. Chem. **8**(6), 531–541 (2016)

- 3. Hao, G.F., Wang, F., Li, H., Zhu, X.L., Yang, W.C., Huang, L.S., Wu, J.W., Berry, E.A., Yang, G.F.: Computational discovery of picomolar Q(o) site inhibitors of cytochrome bc1 complex. J. Am. Chem. Soc. **134**(27), 11168–11176 (2012)

- Forli, S., Huey, R., Pique, M.E., Sanner, M.F., Goodsell, D.S., Olson, A.J.: Computational protein-ligand docking and virtual drug screening with the AutoDock suite. Nat. Protoc. 11(5), 905 (2016)

- 5. Raicu, I.: Falkon: a Fast and Light-weight tasK executiON framework, p. 43 (2007)

- 6. Raicu, I., Zhao, Z., Wilde, M., Foster, I., Beckman, P., Iskra, K., Clifford, B.: Toward loosely coupled programming on petascale systems, pp. 1–12 (2008)

- 7. Jain, A., Ong, S.P., Chen, W., Medasani, B., Qu, X., Kocher, M., Brafman, M., Petretto, G., Rignanese, G.M., Hautier, G.: FireWorks: a dynamic workflow system designed for high-throughput applications. Concurr. Comput. Pract. Exp. 27(17), 5037–5059 (2015)

- 8. Zhou, T., Caflisch, A.: Data management system for distributed virtual screening. J. Chem. Inf. Model. **49**(1), 145–152 (2009)

- Trott, O., Olson, A.J.: AutoDock Vina: improving the speed and accuracy of docking with a new scoring function, efficient optimization, and multithreading. J. Comput. Chem. 31(2), 455–461 (2010)

- 10. Yan, X., Li, J., Liu, Z., Zheng, M., Ge, H., Xu, J.: Enhancing molecular shape comparison by weighted gaussian functions. J. Chem. Inf. Model. **53**(8), 1967–1978 (2013)

- 11. Jones, G., Willett, P., Glen, R.C., Leach, A.R., Taylor, R.: Development and validation of a genetic algorithm for flexible docking. J. Mol. Biol. **267**(3), 727–748 (1997)

- Friesner, R.A., Banks, J.L., Murphy, R.B., Halgren, T.A., Klicic, J.J., Mainz, D.T., Repasky, M.P., Knoll, E.H., Shelley, M., Perry, J.K.: Glide: a new approach for rapid, accurate docking and scoring. 1. Method and assessment of docking accuracy. J. Med. Chem. 47(7), 1739–1749 (2004)

- 13. Rarey, M., Kramer, B., Lengauer, T., Klebe, G.: A fast flexible docking method using an incremental construction algorithm. J. Mol. Biol. **261**(3), 470–489 (1996)

- Yoo, A.B., Jette, M.A., Grondona, M.: SLURM: simple linux utility for resource management. In: Feitelson, D., Rudolph, L., Schwiegelshohn, U. (eds.) JSSPP 2003. LNCS, vol. 2862, pp. 44–60. Springer, Heidelberg (2003). https://doi.org/10.1007/ 10968987 3

- 15. Bode, B., Halstead, D.M., Kendall, R., Lei, Z., Jackson, D.: The Portable batch scheduler and the Maui Scheduler on Linux Clusters (2000)

- Gentzsch, W.: Sun Grid Engine: Towards Creating a Compute Power Grid, pp. 35–36 (2001)

- 17. Thain, D., Tannenbaum, T., Livny, M.: Distributed computing in practice: the Condor experience: research articles. Concurr. Comput. Pract. Exp. 17(2–4), 323–356 (2010)

- Wang, Y., Xiao, J., Suzek, T.O., Jian, Z., Wang, J., Bryant, S.H.: PubChem: a public information system for analyzing bioactivities of small molecules. Nucleic Acids Res. 37 (Web Server issue), W623 (2009)

- 19. Irwin, J.J., Sterling, T., Mysinger, M.M., Bolstad, E.S., Coleman, R.G.: ZINC: a free tool to discover chemistry for biology. J. Chem. Inf. Model. **52**(7), 1757–1768 (2012)

- Gaulton, A., Bellis, L.J., Bento, A.P., Chambers, J., Hersey, A., Light, Y., Mcglinchey, S., Michalovich, D., Allazikani, B.: ChEMBL: a large-scale bioactivity database for drug discovery. Nucleic Acids Res. 40(Database issue), D1100 (2012)

- Chen, J., Swamidass, S.J., Dou, Y., Bruand, J., Baldi, P.: ChemDB: a public database of small molecules and related chemoinformatics resources. Bioinformatics 21(22), 4133–4139 (2005)

- 22. Banker, K.: MongoDB in Action. Manning Publications Co., Greenwich (2011)

- 23. O'Boyle, N.M., Banck, M., James, C.A., Morley, C., Vandermeersch, T., Hutchison, G.R.: Open babel: an open chemical toolbox. J. Cheminform. **3**(1), 1–14 (2011)

- Li, J., Ehlers, T., Sutter, J., Varma-O'Brien, S., Kirchmair, J.: CAESAR: a new conformer generation algorithm based on recursive buildup and local rotational symmetry consideration. J. Chem. Inf. Model. 47(5), 1923–1932 (2007)

- 25. Visualizer, D.S.: Release 3.5. Accelrys Inc., San Diego (2012)

- Jaghoori, M.M., Bleijlevens, B., Olabarriaga, S.D.: 1001 ways to run AutoDock Vina for virtual screening. J. Comput. Aided Mol. Des. 30(3), 1–13 (2016)

**Open Access** This chapter is licensed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license and indicate if changes were made.

The images or other third party material in this chapter are included in the chapter's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the chapter's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder.

# HBasechainDB – A Scalable Blockchain Framework on Hadoop Ecosystem

Manuj Subhankar Sahoo<sup>(⊠)</sup> and Pallav Kumar Baruah

Sri Sathya Sai Institute of Higher Learning, Anantapur 515134, Andhra Pradesh, India subhankar.3eblue@gmail.com, pkbaruah@sssihl.edu.in

**Abstract.** After the introduction of Bitcoin, blockchain has made its way through numerous applications and been adopted by various communities. A number of implementations exist today providing a platform to carry on business with ease. However, it is observed the scalability of blockchain still remains an issue. Also, none of the framework can claim the ability to handle Big Data and support to perform analytics, which is an important and integral facet of current world of business. We propose HBasechainDB, a scalable blockchain-based tamperproofed Big Data store for distributed computing, HBasechainDB adds the blockchain characteristics of immutability and decentralization to the HBase database in the Hadoop ecosystem. Linear scaling is achieved by pushing computation to the data nodes. HBasechainDB comes with inherent property of efficient big data processing as it is built on Hadoop ecosystem. HBasechainDB also makes adaptation of blockchain very easy for those organizations whose business logic are already existing on Hadoop ecosystem. HBasechainDB can be used as a tamper-proof, decentralized, distributed Big Data store.

**Keywords:** Blockchain  $\cdot$  HBase  $\cdot$  Big Data  $\cdot$  Tamperproof Immutability

#### 1 Introduction

A Blockchain is a distributed ledger of blocks which records all the transactions that have taken place. It was first popularized by a person or a group under the pseudonym Satoshi Nakamoto, in 2008 by introducing Bitcoin [11]: A Peerto-Peer Electronic Cash System. This technology revolutionized the decentralized paradigm by introducing and using a Consensus mechanism: Proof-of-Work (PoW). Proof-of-Work defines the requirement of an expensive calculation also called mining, to be performed so as to create a new trustless set of transactions, also called blocks on the blockchain. The major breakthrough for Bitcoin was the hash based blockchain which made the blocks of transactions tamper-proof, transparent and aversive to DoS attack.

Blockchains can support a variety of applications like decentralized financial services, Internet-of-Things [12], smart properties, etc. Several works have centered around the evaluation of potential use cases for the blockchain [3,9,13].

© The Author(s) 2018

R. Yokota and W. Wu (Eds.): SCFA 2018, LNCS 10776, pp. 18–29, 2018. https://doi.org/10.1007/978-3-319-69953-0\_2 Blockchains can also be seen as a tamper-proof, decentralized data store of a variety of data including government deeds, land ownership records, stock market transactions, etc. However, the PoW consensus protocol enforces major performance bottlenecks on the blockchain. Transaction latencies are as high as an hour and the theoretical peak transactions throughput is just 7 transactions per second. Further, the full nodes in the Bitcoin network which are capable of validating blocks and transactions are expected to maintain copies of the entire Bitcoin blockchain. This places heavy storage demands on the participating nodes. The Bitcoin blockchain is about 136 GB at the time of writing [1]. The communication model also places heavy demands on network bandwidth. The Bitcoin blockchain is also not scalable in that an increase in the number of nodes in the Bitcoin network does not help in increasing the network throughput, latency or capacity. As pointed out by Croman et al. [7], with the increasing adoption of blockchains, we need to address concerns about their scalability.

Apart from digital currency, blockchain technology has taken its own way through many types of industries which includes Finance and Accounting, Supply Chain and Logistics, Insurance etc. For example, financial institutions can settle securities in minutes instead of days. Manufacturers can reduce product recalls by sharing production logs with original equipment manufacturers (OEMs) and regulators. Businesses of all types can more closely manage the flow of goods and related payments with greater speed and less risk. For this reason various industries are trying to adopt blockchain for running their business process smoother and faster. Hyperledger Fabric and BigchainDB are the most widely used framework for blockchainifying business processes.

Today's business processes doesn't generate just data, they generates huge amount of data of wide variety with thrilling velocity. After putting these kinds of data on blockchain it is very important to process and analyze these data in an efficient way. Hadoop is a classic ecosystem which provides numerous functionalities with high efficiency for processing and analyzing these kind of data. A lot of business logic already exists in Hadoop ecosystem to process and analyze these data. Therefore it will be much more easier for the industries to adopt blockchain technology if there exists a scalable blockchain framework in Hadoop ecosystem. Towards this end, HBasechainDB is a first step towards providing a scalable blockchain framework in the Hadoop ecosystem. HBasechainDB is started by High performance Computing and Data (HPCD) Group, Department of Mathematics and Computer Science (DMACS), Sri Sathya Sai Institute of Higher Learning. This is achieved by imparting the blockchain characteristics of immutability and decentralization to the HBase database.

# 2 Background and Related Work

A lot of work has been underway for addressing the scalability of blockchains. Vukolic [14] has contrasted PoW-based blockchains to those based on BFT state machine replication for scalability. Eyal et al. [8] introduces Bitcoin-NG as a scalable blockchain protocol based on BFT consensus protocols. These approaches

are focused upon improving the consensus protocol. McConaghy et al. [10] adopted a different approach to scalability. They started with a distributed database, MongoDB, and added the blockchain features of decentralized control, immutability while supporting the creation and movement of digital assets to provide a scalable, decentralized database BigchainDB. The major contribution of BigchainDB that enables this scalability is the concept of blockchain pipelining. In blockchain pipelining, blocks are added to the blockchain without waiting for the current block to be agreed upon by the other nodes. The consensus is taken care of by the underlying database. The validation of blocks is not done during block addition but eventually by a process of voting among nodes. This has huge performance gains and BigchainDB has points to transaction throughputs of over a million transactions per second and sub-second latencies.

In creating HBasechainDB, we have adopted an approach similar to that of BigchainDB. Instead of using MongoDB as the underlying database, we use the Hadoop database, Apache HBase. Apache HBase is a distributed, scalable Big Data store. It supports random, real-time read/write access to Big Data. Apache HBase is an open-source, distributed, versioned, non-relational, column-family oriented database modeled after Google's Bigtable [6]. HBase provides both linear and modular scaling, along with strongly consistent reads/writes. HBase tables are distributed on the cluster via regions. HBase supports automatic sharding by splitting and re-distributing regions automatically as data grows. HBasechainDB is a scalable, decentralized data store akin to BigchainDB.

### 3 Terminology

- Blockchain: A chain of blocks where every block has a hash link to the previous block i.e. every block stores the hash of the previous block. An advantage is, just by storing the hash of the last block we can easily detect if any change has been made to any of the block.

- Double spending: It is an attack where the asset is spent in more than one transaction. To prevent double spending, blockchain framework needs to check whether a particular asset is spent in any of the previous transactions. For instance: user U2 wants to spend/transfer an asset A1, in transaction T2, to another user U3. Say, the asset A1 was transferred to U2 by user U1 in some previous transaction T1. U2 specifies T1's Id in T2, which shows that T1 was the transaction which contained asset A1, and U2 got it from U1. Now, U2 wants to spend/transfer it to U3. So before validating transaction T2 with asset A1, a Blockchain framework checks all the transaction with asset A1 that has occurred/lies in between T1 and T2, in order. If A1 does not occur in any of the transactions then A1 is not double spent else it's double spent.

- Blockchain Pipeline: In Blockchain pipelining, blocks are written to the underlying database without waiting for a vote which confirms the block's validity. Voting for a block and forming a chain happens as a separate layer.

- Changefeed: It is a mechanism by which any update on the Blockchain is notified to the nodes. This automatic change notifications on the Blockchain brings another benefit: they improve tamper-detection (beyond what a blockchain offers). If a hacker somehow manages to delete or update a record in the data store, the hashes change (like any blockchain). In addition, a data-store with automatic change notifications would notify all the nodes, which can then immediately revert the changes and restore the hash integrity.

- **HBase region-server:** These are the basic elements of availability and distribution for tables, and are comprised of a store per Column Family.

- **HBase Master:** Responsible for coordinating Regions in the cluster and execute administrative operations.

#### 4 Architecture

#### 4.1 Data Model of Transaction

The Transaction Model of all Blockchain Platforms has three important fields: Transaction Id, List of Inputs, List of Outputs. Apart from these, there are fields which are platform dependent. HBasechainDB's transaction model consists of; Transaction Id, Asset, List of Inputs, List of Outputs and Metadata.

- 1. **ID:** The transaction Id uniquely identifies the transaction. It is a SHA3-256 hash of the asset, list of inputs, list of outputs and metadata.

- 2. **Asset:** A JSON format document associated with a transaction.

- 3. List of Inputs: Each input in the list of a transaction is spendable/transferable if it has a link to the output of some previous transaction (in case of transfer transaction. Creation transaction doesn't have link to out of any previous transaction). This input is then spent/transferred by satisfying/fulfilling the crypto-conditions on that previous transaction output. A CREATE transaction should have exactly one input. A TRANSFER transaction should have at least one input (i.e. >1).

- 4. **List of outputs:** Each output in the list of a transactions indicates the crypto-conditions which must be satisfied by anyone who wishes to spend/transfer that output to some other transaction. It also indicates the number of shares of the asset tied to that output.

- Metadata: User-provided transaction metadata. It can be any valid JSON document or NULL.

#### 4.2 Design Details

HBasechainDB is a super peer-to-peer network operating using a federation of nodes. All the nodes in the federation have equal privileges which gives HBasechainDB its decentralization. Such a super peer-to-peer network was inspired by the Internet Domain Name System. Any client can submit or retrieve transactions or blocks, but only the federation nodes can modify the blockchain. The federation can grow or shrink during the course of operation of

HBasechainDB. Let us say there are n federation nodes N1, N2, ..., Nn. When a client submits a transaction t, it is assigned to one of the federation nodes, say Nk. The node Nk is now responsible for entering this transaction into the blockchain. Nk first checks for the validity of the transaction. Validity of a transaction includes having a correct transaction hash, correct signatures, existence of the inputs to the transaction, if any, and the inputs not having been already spent. Once Nk has validated a set of transactions, it bundles them together in a block, and adds it to the blockchain. Any block can only contain a specified maximum number of transactions. Let us say t was added in the block B.

When the block B is added to the blockchain its validity is undecided. Since the federation is allowed to grow or shrink during the operation of HBasechainDB, blocks also include a list of voters based on the current federation. All the nodes in the voter list for a block vote upon B for its validity. For voting upon a block, a node validates all the transactions in the block. A block is voted valid only if all the transactions are found to be valid, else it is voted invalid. If a block gathers a majority of valid or invalid votes, its validity changes from undecided to valid or invalid respectively. Only the transactions in a valid block are considered to have been recorded in the blockchain. The ones in the invalid blocks are ignored altogether. However, the chain retains both valid and invalid blocks. A block being invalid does not imply that all the transactions in the block are invalid. Therefore, the transactions from an invalid block are re-assigned to federation nodes to give the transactions further chance of inclusion in the blockchain. The reassignment is done randomly. This way, if a particular rogue node was trying to add an invalid transaction to the blockchain, this transaction will likely be assigned to a different node the second time and dropped from consideration. Thus, if block B acquires a majority of valid votes, then transaction t would have been irreversibly added to the blockchain. On the other hand, if B were invalid, then t would be reassigned to another node and so on until it is included in the chain or removed from the system.

As discussed in the previous section, the chain is not formed when blocks are created. When a block is entered into hbasechain table, the blocks are stored in HBase in the lexicographical order of their ids. The chain is actually formed during vote time. When a node votes on a block, it also specifies the previous block that it had voted upon. Thus, instead of waiting for all the federation nodes to validate the current block before proceeding to the creation of a new block, blocks are created independent of validation. This is the technique of blockchain pipelining described earlier. Over time, the blockchain accumulates a mix of valid and invalid blocks. The invalid blocks are not deleted from the chain to keep the chain immutable. What we also note here is that while it would seem that different nodes could have a different view of the chain depending upon the order in which they view the incoming blocks, it is not seen in practice in HBasechainDB due to the strong consistency of HBase and the fact that the blocks to be voted upon are ordered based on their timestamp. Thus, each node sees the same order of blocks, and we have the same chain view for different nodes.

To tamper with any block in the blockchain, an adversary will have to modify the block, leading to a change in its hash. This changed hash would not match the vote information for the block in the votes table, and also in subsequent votes that refer to this block as the previous block. Thus an adversary would have to modify the vote information all the way up to the present. However, we require that all the votes being appended by nodes are signed. Thus, unless an adversary can forge a node's signature, which is cryptographically hard, he cannot modify the node's votes. In fact, he has to forge multiple signatures to affect any change in the blockchain preventing any chances of tampering. This way HBasechainDB provides a tamper-proof blockchain over HBase.

#### 4.3 Exploiting HBase

In this section we describe the distinction between MongoDB and HBase. We also justify the means to achieve greater performance with the proposed system design.

MongoDB is a document store database. A document is a big JSON block with no particular schema or format. This gives an edge to dynamic use cases and ever-changing applications. MongoDB does not provide triggers. Although MongoDB has its own advantages, the document store characteristic of MongoDB degrades its performance for following operations:

- 1. Working with individual columns.

- 2. Performing join operations.

HBase is a wide column store database. It is a distributed, scalable, reliable, and versioned storage system capable of providing random read/write access in real-time. It provides a fault-tolerant way of storing large quantities of sparse data. HBase features compression, in-memory operation and Bloom filters on a per-column basis.

#### We use the following characteristics of HBase extensively to derive performance:

- 1. HBase is partitioned to tables, and tables are further split into column families. Column families must be declared in the schema, and we can group certain set of columns together. One of the major operations in blockchain transaction is checking for Double-Spending. In order to make the check for double spending more efficient, we can keep the input column of all these transactions in a separate column family. This will allow us to perform the check for double spending faster because the region server will need to load only one column family which contains the input of the transaction. In case of database such as MongoDB the database server needs to load the whole document before filtering out the input column and performing Double Spent check.

- 2. HBase is optimized for reads, supported by single-write master, which results in a strict consistency model. And use of Ordered Partitioning supports rowscans. In Blockchain we need one write and many read operation because

- the transactions are written only once but read many times for various purposes like checking double spending and performing checks on whether any tampering took place.

- 3. HBase provides us with various ways in which we can run our custom code on the region-server. HBase co-processor and custom filters are two such ways. HBase co-processor can act as database triggers. In our implementation we use these features in following ways:

- (a) The check for double spending is generally done by loading the transactions to the federation nodes (i.e. the client system). Loading this many transactions from region-server to the federations node system is a major bottleneck for the system throughput. In our approach, instead of pulling the data required for double spending check on to the client-system, we push the computation check to the region-server using HBase custom filter. This approach improves the performance in two ways:

- Data does not move towards the computation node rather computation moves towards the Data node. Since the code size is exponentially lesser than data size, we improve the system by decreasing the communication time.

- ii. Computation for double spending is done in parallel on multiple region-server compared to the traditional approach of checking on a single Client node.

- (b) Changefeed brings a great benefit to the Blockchain framework. We use HBase co-processor to implement changefeed which will notify immediately whenever a hacker tries to change or delete the content of the database.

## 5 Implementation Details

The Federation Nodes in HBasechainDB are initialized with a key-pair; Ed25519 [2,4] signing system. SHA3-256 [5] hashing scheme is used for hashing the transactions and blocks. The current implementation of HBasechainDB uses six HBase tables. A critical issue in the current design of HBase tables is that of designing the row key, since the region splits and the scans on HBase tables are done in the lexicographical order of the row key. The row key pattern depends upon the access pattern for the data in the Hbase table.

Following is the description of the HBase tables:

1. backLog: When a transaction is submitted to the Federation nodes, the transaction is randomly assigned to one of the nodes. All such assigned transactions are stored in the backlog table with each transaction stored in a single row. A node scanning the backlog table should only have to read the transactions assigned to itself. Thus, the first segment of the row key for backlog table is the public key of the node to whom the transaction was assigned, to ensure that a node can scan the backlog table with the row prefix being its own public key. The last segment of the row key contains the transaction reference id. So the row key looks like: <publicKey>\_<transactionId>

- 2. block: This is the table that contains all the blocks in the blockchain. Each block is a logical block which contains only the id's of the transaction which are present in the block. The actual transaction details are stored in "hbasechaindb" table. Since the access pattern for this table is looking up blocks based on block id, the row key for this table is just the block id: <blockId>

- 3. hbasechaindb: This is the table where all the transaction details are stored after a transaction is put on the blockchain. In this table each row corresponds to a single transaction. Since the access pattern for this table is looking up transaction based on transaction link id, the row key of this table is <transaction link id>. The transaction link id consists of <br/> <br/>block\_id>\_<transaction\_id>. This transaction link id which is of previous output is used in inputs of current transaction while spending an asset

- 4. toVote: Every new block created has to be voted upon by the Federation nodes. For this, we need to inform the Federation nodes of their need to vote upon a newly created block. To this end, every block created is added to this table to signal the node for voting. It is removed from the table once the node has finished voting on it. The row key of this table is: <federation node's signing key>\_<block id>

- 5. vote: This is the table in which all the votes are recorded. There has to be an entry for every federation node which votes for their respective blocks. The row key of the table is: <block\_id>\_<decision>\_<Fed. Node public key>

- 6. reference: This is the table which stores the map between transaction link id and transaction id. This table acts as an index when the details of a transaction is queried. Since the access pattern of the table is transaction reference id, the row key of this table is just the transaction reference id: <transacation\_link\_Id>

When a transaction is submitted to HBasechainDB, it is first put in the <code>backLog</code> table. Federation nodes picks the transactions from <code>backLog</code> table in certain time interval, checks the validity of the transactions, bundles them into blocks and adds those blocks to the Blockchain. As show in Fig. 1, when a federation node forms a block, it updates 3 HBase tables. In <code>block</code> table, the transaction.Id of all the transactions are made as separate blocks and stored. In the <code>bbasechaindb</code> table, all the transaction details are stored. In the <code>toVote</code> table the information about newly created block is stored. The federation nodes refers this <code>toVote</code> table to vote for the block. All the Federation nodes, in certain time interval checks the <code>toVote</code> table and cast their vote after checking the validity of the block. All the votes are stored in the <code>vote</code> table. After the validity of a block, entries corresponding to all the transactions are made in the <code>reference</code> table.

The complete implementation of HBasechainDB is done using Java since the performance of HBase API for Java is best among the HBase API's present for different languages. HBase API for Java also gives advantage of writing custom filters and coprocessors.

Fig. 1. Transaction flow of HBasechainDB

#### 6 Performance

#### 6.1 Experimental Setup

We have used three nodes for the initial performance testing of HBasechainDB with the following configurations:

- 3 nodes with Intel Core i5-4670 CPU @ 3.40 GHz\*4 processor and 16 GB of memory, with Ubuntu 16.04 OS.

- Each of the 3 nodes runs HBase region-server. There is a HBase master running in one of the system.

- There is a Replication factor of 3 for the underlying HDFS.

- The HBase is backed by 3 quorum zookeeper.

- We consider only creation of transactions for our case.

#### 6.2 Results

We have tested HBasechainDB for scalability over three nodes. There are two parameters that we describe the performance of HBasechainDB with:

- Transaction Latency: This is defined as the time elapsed since the submission of a transaction to HBasechainDB until the block in which it has been recorded is validated. The transaction latency is found for streaming transactions.

- Throughput: This is the number of transactions that are recorded in the blockchain per second. To find the peak throughput the blockchain is capable of, we store the transactions in the backlog beforehand and then run the nodes. The throughput observed then is the peak throughput.

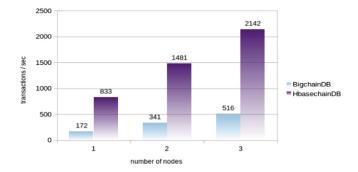

${\bf Fig.\,2.}$  Performance of Bigchain DB and HBasechain DB

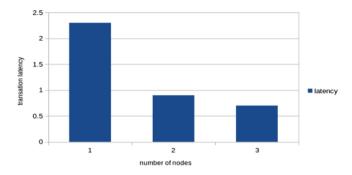

Fig. 3. Latency of HBasechainDB in sec.

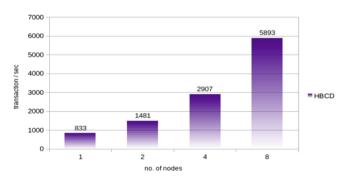

Fig. 4. Scalability of HBasechainDB upto 8 nodes

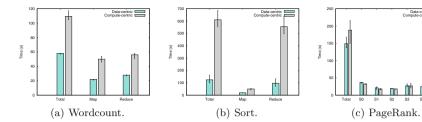

Figure 2 compares the transaction throughput of HBasechainDB and BigchainDB, using systems with 1, 2 and 3 nodes and Fig. 3 shows the latency of HBasechainDB. Figure 4 shows the scalability of HBasechainDB till 8 nodes. The result shows, as we add the nodes the transaction throughput of HBasechainDB scales linearly.

The main reason behind the linear scale of HBasechainDB is, almost all the computation which includes *computation for transaction's validity* and *check for double spending* is pushed to server side. Therefore if we increase the HBase nodes keeping the federation node constant, the system scales linearly.

# 7 Conclusion

Blockchain technologies can be very useful in the Big Data scenario by helping us immutably record data and decentralizing data services. However, current blockchain implementations with their extremely low transaction throughputs and high transaction latencies do not lend themselves to Big Data. Discussions on improving blockchain scalability have largely focused on using better consensus protocols as against the PoW protocol used by Bitcoin. BigchainDB provides an alternative idea where instead of scaling blockchains to provide scalable data stores, they implement a blockchain over an existing scalable distributed database. Such an implementation inherits the scalability of the underlying database, while adding the immutability and decentralization offered by blockchains. While BigchainDB was implemented upon the MongoDB and Rethink DB database, with our work we provide an alternate implementation over HBase. HBasechainDB is an hitherto unavailable blockchain implementation integrated with the Hadoop ecosystem. It supports very high transaction throughputs with sub-second latencies and the creation and movement of digital assets. HBasechainDB scales linearly and also is good platform for analyzing data that are present on blockchain.

**Acknowledgments.** Our work is dedicated to Bhagawan Sri Sathya Sai Baba, Founder Chancellor of Sri Sathya Sai Institute of Higher Learning. We acknowledge Adarsh Saraf from IBM Research, Bengaluru, India, who has initiated this work. We thank him for his inspiration and motivation. We also acknowledge Maestro Technology, USA for their help and support.

# References

- 1. https://blockchain.info/charts/blocks-size

- 2. https://github.com/str4d/ed25519-java/tree/master/src/net/i2p/crypto/eddsa

- 3. Aron, J.: Automatic world (2015)

- Bernstein, D.J., Duif, N., Lange, T., Schwabe, P., Yang, B.-Y.: High-speed high-security signatures. J. Cryptographic Eng. 2(2), 1–13 (2012)

- Bertoni, G., Daemen, J., Peeters, M., Van Assche, G.: Keccak specifications. Submission to NIST (Round 2) (2009)

- Chang, F., Dean, J., Ghemawat, S., Hsieh, W.C., Wallach, D.A., Burrows, M., Chandra, T., Fikes, A., Gruber, R.E.: Bigtable: a distributed storage system for structured data. ACM Trans. Comput. Syst. (TOCS) 26(2), 4 (2008)

- Croman, K., et al.: On scaling decentralized blockchains. In: Clark, J., Meiklejohn, S., Ryan, P.Y.A., Wallach, D., Brenner, M., Rohloff, K. (eds.) FC 2016. LNCS, vol. 9604, pp. 106–125. Springer, Heidelberg (2016). https://doi.org/10.1007/978-3-662-53357-4-8

- 8. Eyal, I., Gencer, A.E., Sirer, E.G., Van Renesse, R.: Bitcoin-NG: a scalable blockchain protocol. In: NSDI, pp. 45–59 (2016)

- 9. Liebenau, J., Elaluf-Calderwood, S.M.:. Blockchain innovation beyond bitcoin and banking (2016)

- McConaghy, T., Marques, R., Müller, A., De Jonghe, D., McConaghy, T., McMullen, G., Henderson, R., Bellemare, S., Granzotto, A.: BigchainDB: a scalable blockchain database. White paper, BigChainDB (2016)

- 11. Nakamoto, S.: Bitcoin: A Peer-to-Peer Electronic Cash System (2008)

- Panikkar, S., Nair, S., Brody, P., Pureswaran, V.: Adept: an IoT practitioner perspective. IBM Institute for Business Value (2014)

- Swan, M.: Blockchain: Blueprint for a New Economy. O'Reilly Media Inc., Sebastopol (2015)

- 14. Vukolić, M.: The quest for scalable blockchain fabric: proof-of-work vs. BFT replication. In: Camenisch, J., Kesdoğan, D. (eds.) iNetSec 2015. LNCS, vol. 9591, pp. 112–125. Springer, Cham (2016). https://doi.org/10.1007/978-3-319-39028-4\_9

Open Access This chapter is licensed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license and indicate if changes were made.

The images or other third party material in this chapter are included in the chapter's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the chapter's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder.

# DETOUR: A Large-Scale Non-blocking Optical Data Center Fabric

Jinzhen Bao<sup>1,2</sup>, Dezun Dong<sup>2(⊠)</sup>, and Baokang Zhao<sup>2</sup>

PLA Academy of Military Science, Beijing, China

National University of Defense Technology, Changsha, China {baojinzhen,dong,bkzhao}@nudt.edu.cn

Abstract. Optical data center networks (DCNs) are attracting growing interest due to the technical strength compared to traditional electrical switching networks, which effectively eliminates the potential hotspot caused by over-subscription. However, the evolving traffics with high fan-out and various patterns pose new challenges to optical DCNs. Prior solutions are either hard to support high fan-out communications in large-scale or suffer from limited connections with low performance.

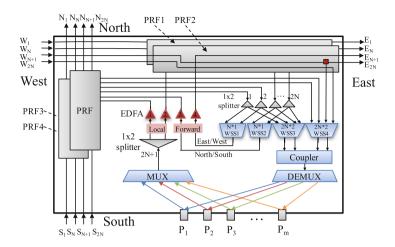

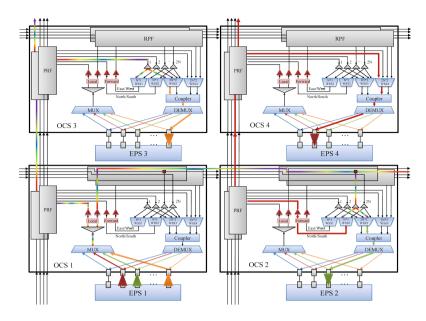

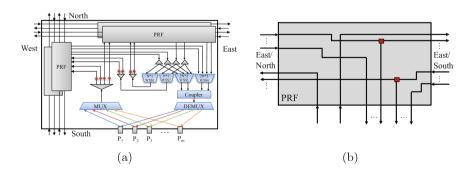

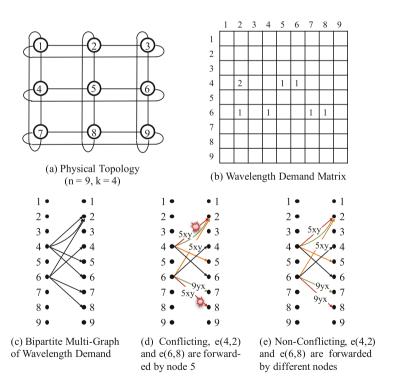

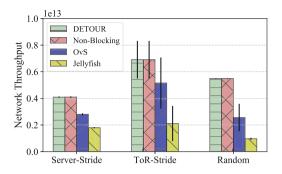

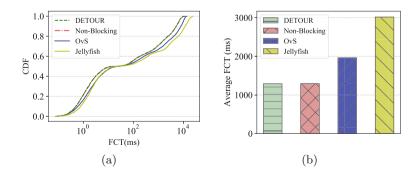

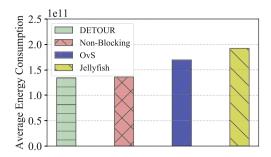

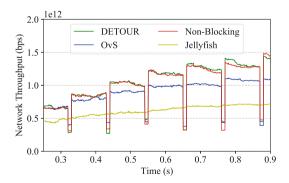

In this paper we propose DETOUR, a large-scale non-blocking optical switching data center fabric. DETOUR composes of optical circuit switches (OCSes) and connects them in a 2D-Torus topology. It supports up to 729 racks and 69K+ ports with each OCS having 96 wavelengths. DETOUR utilizes a broadcast-and-select mechanism and enables signals optically forwarded to any dimension. Moreover, it realizes non-blocking by recursively adjusting conflict links between the diagonal forwarding OCSes. Our extensive evaluation results show that DETOUR delivers comparable high performance to a non-blocking optical switching fabric. It outperforms up to  $2.14\times$  higher throughput, and reduces 34% flow completion times (FCT) and 21% energy consumption compared with the state-of-the-art works.

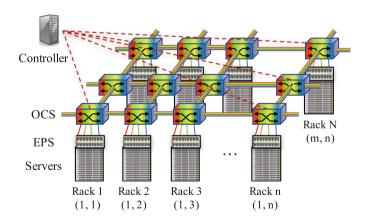

# 1 Introduction

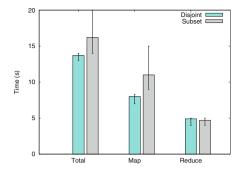

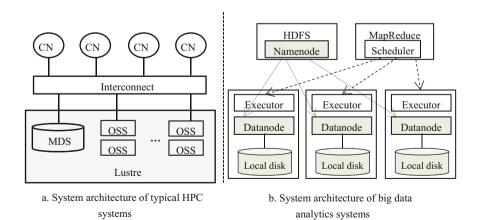

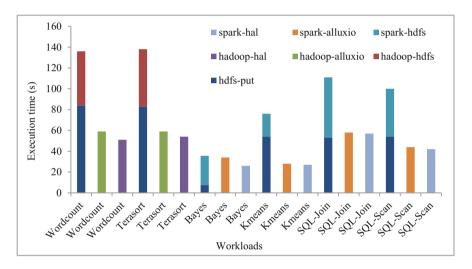

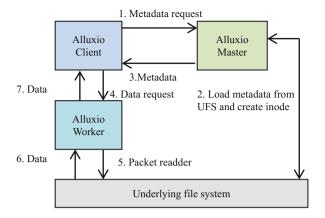

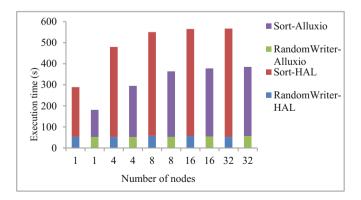

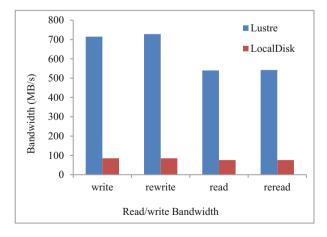

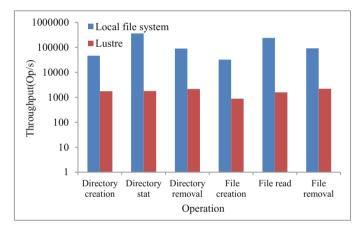

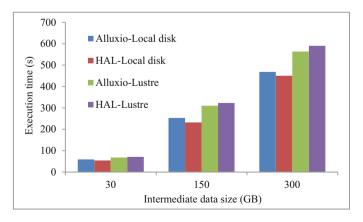

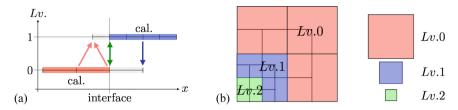

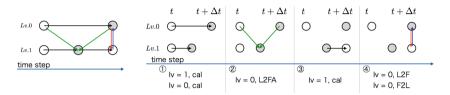

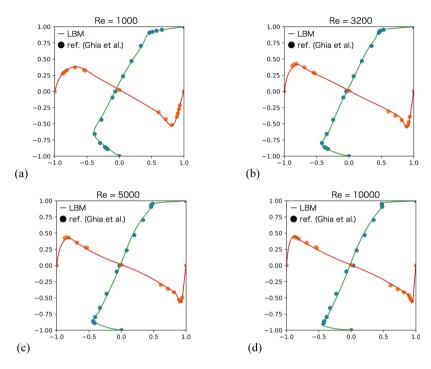

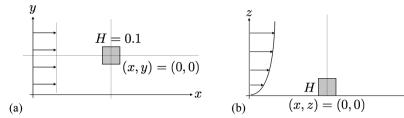

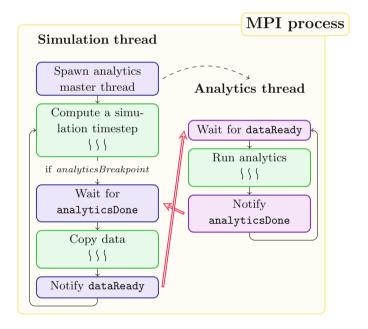

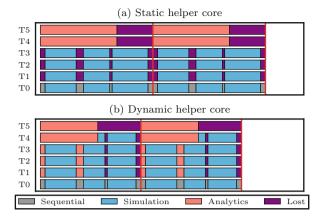

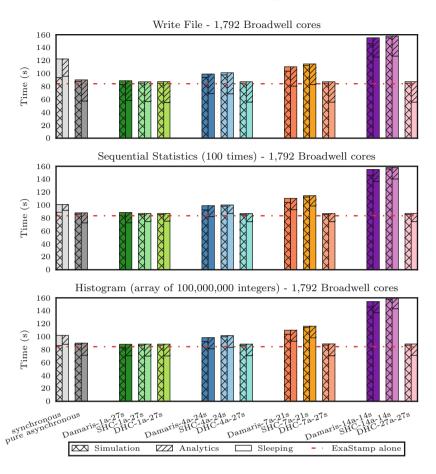

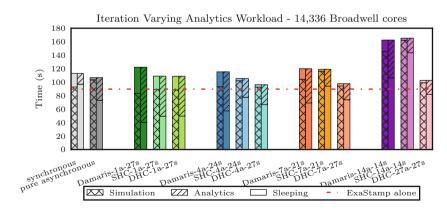

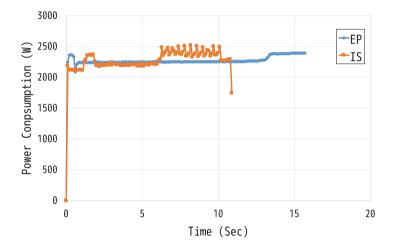

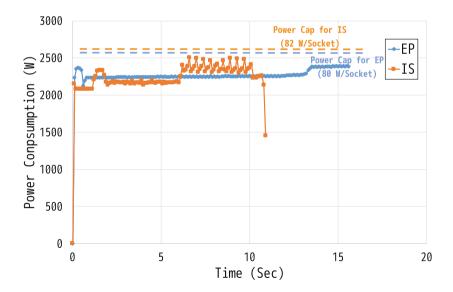

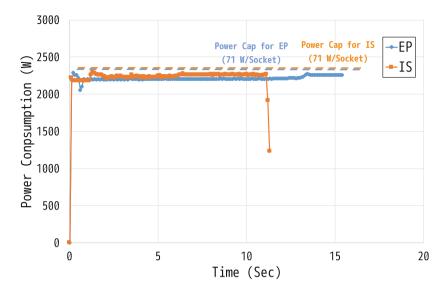

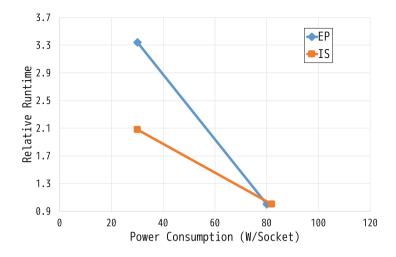

Data centers as the infrastructure of cloud computing, are rapidly expanded to meet the increasing demand of cloud services, big data and high performance applications. Many novel network architectures have been proposed to efficiently connect tens of thousands servers inside data centers. Pure electrical switching architectures, such as Fat-Tree [4], BCube [13] and Jellyfish [20], provide static and uniform interconnections among servers, without considering the dynamic traffic patterns. Due to the mismatch between the static interconnections and the dynamic network traffic, pure electrical switching networks must pay extremely high cost and complex wiring to deliver high bisection bandwidth.